# IMPLEMENTATION OF A RADIATION-TOLERANT COMPUTER BASED ON A LEON3 ARCHITECTURE

by

David Lee Douglas Turner

A thesis submitted in partial fulfillment of the requirements for the degree

of

Master of Science

in

**Electrical Engineering**

MONTANA STATE UNIVERSITY Bozeman, Montana

July, 2015

# ©COPYRIGHT

by

David Lee Douglas Turner

2015

All Rights Reserved

### ACKNOWLEDGEMENTS

I would like to thank my parents for their continual support and for always being there for me, my advisor Brock LaMeres for his guidance and support, and my labmates Sam Harkness and Justin Hogan for their help and advice. I would like to especially thank Ray Weber, the wizard of FPGA design. Without his assistance this project may never have been completed at all.

## TABLE OF CONTENTS

| Introduction       1         Computing Requirements of Future Space Missions       2         The Benefits of the LEON3 Processor       3         The Problem of Radiation in Space       3         Sources of Ionizing Radiation       5         Causes of Variations in Radiation Levels       7         Types of Radiation-induced Damage       9         2. TRADITIONAL SOLUTIONS FOR RADIATION       12         Shielding       12         Circuit Level Solutions       13         3. EMERGING SOLUTIONS FOR RADIATION       17         FPGAs and Triple Modular Redundancy.       17         Partial Reconfiguration and Scrubbing       18         Custom FPGAs with Standard Processors       20         Standard FPGAs with Custom Processors       21         3. MSU'S APPROACH TO RADIATION TOLERANCE       23         Previous Work with MicroBlaze and Virtex-6       23         Current Fault Radiation Tolerance Software       29         Fault Tolerance Test Flights       31         Transition to LEON3 and Artix-7       34         The Artix-7 FPGA       35         4. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE       36         Cobham Gaisler Components       38         LEON Implementation Instructions <t< th=""><th>1.</th><th>BACKGROUND AND MOTIVATION</th><th>1</th></t<> | 1. | BACKGROUND AND MOTIVATION                                                                                                                                                                                | 1                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Shielding12Circuit Level Solutions133. EMERGING SOLUTIONS FOR RADIATION17FPGAs and Triple Modular Redundancy.17Partial Reconfiguration and Scrubbing18Custom FPGAs with Standard Processors20Standard FPGAs with Custom Processors213. MSU'S APPROACH TO RADIATION TOLERANCE23Previous Work with MicroBlaze and Virtex-623Current Fault Radiation Tolerance Software29Fault Tolerance Test Flights31Transition to LEON3 and Artix-734The Artix-7 FPGA354. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE36Cobham Gaisler Components38LEON Implementation Instructions395. EXPERIMENTAL RESULTS41Single Core LEON42Four Core LEON44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | Computing Requirements of Future Space Missions<br>The Benefits of the LEON3 Processor<br>The Problem of Radiation in Space<br>Sources of Ionizing Radiation<br>Causes of Variations in Radiation Levels | 2<br>3<br>5<br>7  |

| Circuit Level Solutions       13         3. EMERGING SOLUTIONS FOR RADIATION       17         FPGAs and Triple Modular Redundancy.       17         Partial Reconfiguration and Scrubbing       18         Custom FPGAs with Standard Processors       20         Standard FPGAs with Custom Processors       21         3. MSU'S APPROACH TO RADIATION TOLERANCE.       23         Previous Work with MicroBlaze and Virtex-6       23         Current Fault Radiation Tolerance Software       29         Fault Tolerance Test Flights.       31         Transition to LEON3 and Artix-7       34         The Artix-7 FPGA.       35         4. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE       36         Cobham Gaisler Components.       38         LEON Implementation Instructions       39         5. EXPERIMENTAL RESULTS       41         Single Core LEON.       42         Four Core LEON.       44                                                                                                                                                                                                                                                                                                                                                                                             | 2. | TRADITIONAL SOLUTIONS FOR RADIATION                                                                                                                                                                      | .12               |

| FPGAs and Triple Modular Redundancy.       17         Partial Reconfiguration and Scrubbing       18         Custom FPGAs with Standard Processors       20         Standard FPGAs with Custom Processors       21         3. MSU'S APPROACH TO RADIATION TOLERANCE.       23         Previous Work with MicroBlaze and Virtex-6       23         Current Fault Radiation Tolerance Software       29         Fault Tolerance Test Flights       31         Transition to LEON3 and Artix-7       34         The Artix-7 FPGA       35         4. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE       36         Cobham Gaisler Components       38         LEON Implementation Instructions       39         5. EXPERIMENTAL RESULTS       41         Single Core LEON       42         Four Core LEON       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                                                                                                                                                                                          |                   |

| Partial Reconfiguration and Scrubbing18Custom FPGAs with Standard Processors20Standard FPGAs with Custom Processors213. MSU'S APPROACH TO RADIATION TOLERANCE23Previous Work with MicroBlaze and Virtex-623Current Fault Radiation Tolerance Software29Fault Tolerance Test Flights31Transition to LEON3 and Artix-734The Artix-7 FPGA354. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE36Cobham Gaisler Components38LEON Implementation Instructions395. EXPERIMENTAL RESULTS41Single Core LEON42Four Core LEON44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3. | EMERGING SOLUTIONS FOR RADIATION                                                                                                                                                                         | .17               |

| Previous Work with MicroBlaze and Virtex-623Current Fault Radiation Tolerance Software29Fault Tolerance Test Flights31Transition to LEON3 and Artix-734The Artix-7 FPGA354. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE36The LEON3 Architecture36Cobham Gaisler Components38LEON Implementation Instructions395. EXPERIMENTAL RESULTS41Single Core LEON42Four Core LEON44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | Partial Reconfiguration and Scrubbing<br>Custom FPGAs with Standard Processors                                                                                                                           | .18<br>.20        |

| Current Fault Radiation Tolerance Software29Fault Tolerance Test Flights31Transition to LEON3 and Artix-734The Artix-7 FPGA354. FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE36The LEON3 Architecture36Cobham Gaisler Components38LEON Implementation Instructions395. EXPERIMENTAL RESULTS41Single Core LEON42Four Core LEON44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3. | MSU'S APPROACH TO RADIATION TOLERANCE                                                                                                                                                                    | .23               |

| The LEON3 Architecture36Cobham Gaisler Components38LEON Implementation Instructions395. EXPERIMENTAL RESULTS41Single Core LEON42Four Core LEON44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | Current Fault Radiation Tolerance Software<br>Fault Tolerance Test Flights<br>Transition to LEON3 and Artix-7                                                                                            | .29<br>.31<br>.34 |

| Cobham Gaisler Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4. | FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE                                                                                                                                                        | .36               |

| Single Core LEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | Cobham Gaisler Components                                                                                                                                                                                | .38               |

| Four Core LEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5. | EXPERIMENTAL RESULTS                                                                                                                                                                                     | .41               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | Four Core LEON                                                                                                                                                                                           | .44               |

# TABLE OF CONTENTS – CONTINUED

| Four Core, Reconfigurable LEON with Triple Modular Redundancy                                                      | 49 |

|--------------------------------------------------------------------------------------------------------------------|----|

| Future Four Tile, Reconfigurable Design                                                                            | 55 |

| FPGA Resource Usage and Configuration Timing                                                                       | 55 |

| Commentary on Partial Reconfiguration and Resource Usage                                                           |    |

| 6. FUTURE WORK                                                                                                     |    |

| REFERENCES CITED                                                                                                   | 60 |

| APPENDICES                                                                                                         |    |

| APPENDIX A: Detailed Instructions for LEON                                                                         |    |

| APPENDIX B: Additional Instructions for LEON3 on Virtex-6<br>APPENDIX C: Quad-core LEON (TMR with Spare) VHDL Code |    |

## LIST OF TABLES

| Page                    |                                                                                                   | Table |

|-------------------------|---------------------------------------------------------------------------------------------------|-------|

| nd their energies [10]6 | 1. A listing of the major types of radiation and the                                              |       |

| 1 0                     | 2. A listing of the different systems implemented and their various characteristics (*estimated). |       |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

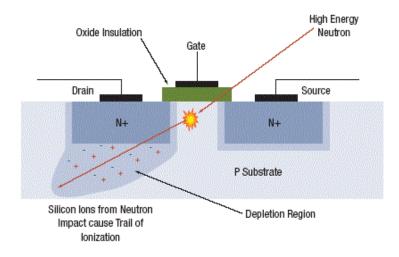

| 1. An example of an ionizing radiation strike that can cause corruption of data in a space-borne computer system [6]4                                                                                                                              |

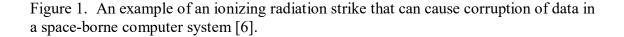

| <ol> <li>Approximate locations of the inner (red) and outer (blue) Van Allen Radiation<br/>Belts around Earth. These belts protect electronics on Earth from most of the<br/>dangerous radiation found in space. Image Credit: NASA. [7]</li></ol> |

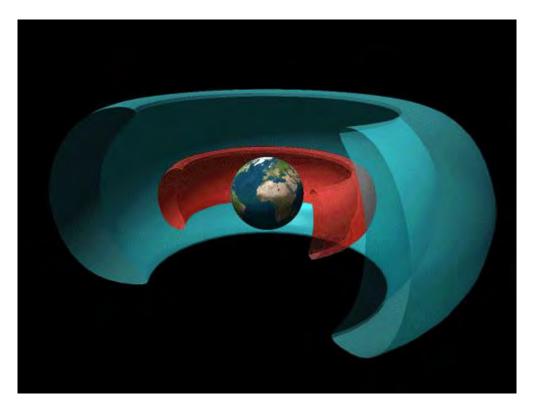

| <ol> <li>Depiction of ion strike at a p-n junction creating separated charge carriers that,<br/>depending on other conditions, could cause one of the various types of Single<br/>Event Effects [8]</li></ol>                                      |

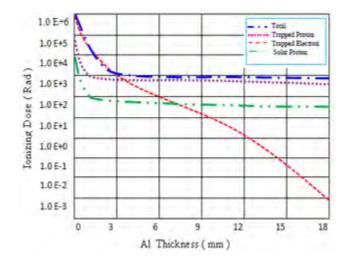

| 4. Ionizing dose vs. Aluminum shielding thickness. Total dose cannot practically be reduced below a certain level, no matter how much shielding is added [16]12                                                                                    |

| 5. Example of radiation hardening by design, wherein a "guard ring" is placed around part of the transistor [9]14                                                                                                                                  |

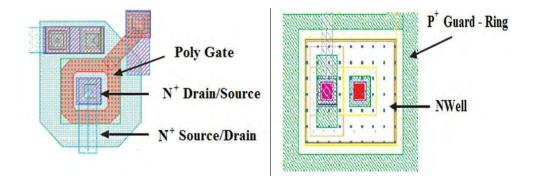

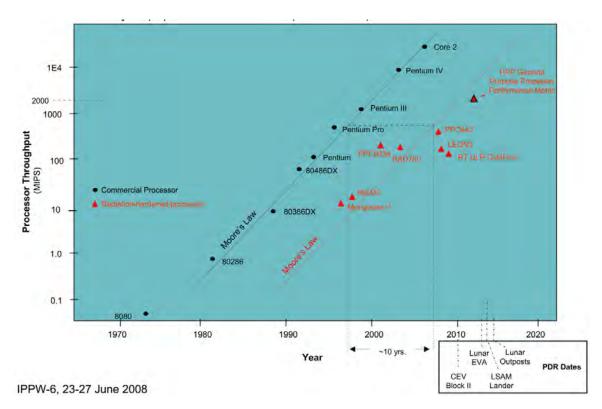

| <ol> <li>Although they also follow Moore's Law, radiation-hardened processors lag<br/>approximately ten years behind general purpose processors in terms of<br/>performance [18]</li></ol>                                                         |

| 7. Basic setup of a triple-modular-redundant RHBA design [10]16                                                                                                                                                                                    |

| <ol> <li>Introducing repair of faulted processor (green dots) greatly increases<br/>reliability over simple triple modular redundancy (blue line) [10]19</li> </ol>                                                                                |

| 9. Virtex-5QV FPGA, the best rad-hard FPGA that money can buy [11]20                                                                                                                                                                               |

| 10. Hardware stack used by the MSU research team [10]24                                                                                                                                                                                            |

| 11. Exploded CAD view of the MSU hardware stack [17]25                                                                                                                                                                                             |

| 12. Block diagram of the MSU hardware stack [17]26                                                                                                                                                                                                 |

| <ol> <li>FPGA board containing the main and control FPGAs used on previous<br/>flights [17]27</li> </ol>                                                                                                                                           |

| 14. Radiation sensor and board developed by MSU [10]29                                                                                                                                                                                             |

# LIST OF FIGURES – CONTINUED

| Figure Page                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------|

| 15. The nine-tile TMR setup currently employed by the MSU system [10]30                                                   |

| 16. NASA-funded sounding rocket that sent the MSU radiation tolerant<br>computer to space in October 2014 [20]            |

| 17. Sample screenshot of the GUI used to view MSU flight data33                                                           |

| <ol> <li>18. An AC701 development board identical to the one used for this project</li> <li>[12]</li></ol>                |

| 19. Block diagram of a full LEON3 processor including peripherals [14]36                                                  |

| 20. Diagram of a LEON3 CPU [14]                                                                                           |

| 21. Block diagram of a single core LEON processor42                                                                       |

| 22. Resource usage of a single core LEON processor on Artix-7 FPGA42                                                      |

| 23. Implemented single core LEON processor on Artix-7 FPGA43                                                              |

| 24. Block diagram of a four-core LEON processor                                                                           |

| 25. Resource usage of a four-core LEON processor on Artix-7 FPGA44                                                        |

| 26. Implemented four-core LEON processor on Artix-7 FPGA45                                                                |

| 27. Block diagram of a four-core, partially reconfigurable LEON processor46                                               |

| 28. Resource usage of a four-core, partially reconfigurable LEON processor<br>on Artix-7 FPGA47                           |

| 29. Implemented four-core, partially reconfigurable LEON processor on<br>Artix-7 FPGA                                     |

| 30. Diagram of modified LEON3 with voter and TMR+spare architecture49                                                     |

| 31. Resource usage of a four-core, partially reconfigurable LEON processor with triple modular redundancy on Artix-7 FPGA |

# viii

# LIST OF FIGURES – CONTINUED

| Figure                                                                                           | Page |

|--------------------------------------------------------------------------------------------------|------|

| 32. Implemented four-core, reconfigurable LEON with TMR on Artix-7 board                         | 52   |

| 33. Resource usage of a single reconfigurable CPU occupying two clock<br>regions on Artix-7 FPGA | 53   |

| 34. Upon interruption, all four cores of LEON are shown to be executing the same instruction     | 54   |

### ABSTRACT

It is desired to create an inexpensive, open-source, radiation-tolerant computer for space applications using commercial, off-the-shelf parts and a proven space-grade processor. Building upon previous work to develop the triplicate architecture using MicroBlaze soft-processors, this implementation, using a modification of the popular open-source space-grade LEON3 soft processor from Cobham Gaisler, enables more compatibility with NASA and existing space computing resources. A partially reconfigurable, triple modular redundant LEON3 processor was successfully implemented in a four-core design on an Artix-7 Field Programmable Gate Array to demonstrate an inexpensive and open-source method of developing radiation-hardened-by-architecture computer systems.

#### BACKGROUND AND MOTIVATION

### Introduction

As the computing requirements of future space missions grow, it has become increasingly enticing to meet these demands with a solution that is inexpensive, easily modifiable, and which provides increased computation. Traditionally, custom radiationhardened Application-Specific Integrated Circuits (ASICs) have been used for spaceborne computers, but these have three significant problems. First of all, low production volumes leads to them being very expensive. Second of all, the physical processes used to make them radiation-hardened tend to lag many years behind cutting-edge computing advancements, which greatly limits their computing power. Third, the reliance on ASICs means that it is much more difficult and time-consuming to upgrade and modify the computer. A less expensive and more powerful computer with a shorter lead time is the ideal solution to this problem.

This thesis presents a solution in the form of a radiation-tolerant architecture running the LEON3 soft-core processor on a Field Programmable Gate Array (FPGA). Solutions of this form do currently exist, but require either expensive custom-made hardware or expensive proprietary software. The LEON3 processor, on the other hand, is an open-source SPARC V8-compliant soft-core processor created by the European Space Agency and further developed and maintained by Cobham Gaisler, a European-based software company. Already used in several space missions, LEON is an ideal soft processor for creating a radiation-hardened FPGA design. A radiation-hardened version, LEON3FT, can be purchased from Cobham Gaisler, but is expensive and not opensource. Therefore, it was decided to take the open-source version, LEON3, and modify it to make a low cost, radiation-tolerant soft processor.

#### Computing Requirements of Future Space Missions

Modern day space missions carry a host of sensors and payloads that can require substantial computing resources. For example, a SpaceX Dragon capsule carries as many as 54 separate processors. This includes 18 different units, each with three processors to increase reliability. To save cost, these processors are not individually radiationhardened, and therefore have to be used in sets of three, which drastically increases the number of processors in use [21]. Another reason to increase computing resources on spacecraft is to perform more data analysis onboard. This allows less data to be streamed back to the ground for human analysis, increasing the potential scientific and engineering benefits of a mission without requiring more downlink bandwidth [17].

Furthermore, as spaceflight moves toward becoming reusable and inexpensive, there will be additional pressure to create less expensive payloads that can use off-theshelf parts and have a shorter lead time for upgrades. This creates an ideal environment for the use of FPGAs, on which fault tolerance can be implemented inexpensively, and which can be modified quickly and without the need for new hardware. Unlike ASICs, FPGAs can be used to create fault-tolerant computers in an off-the-shelf configuration, wherein inexpensive, mass-produced hardware is used and the only modifications necessary are software-related. This allows for more modern, high-performance

hardware to be used, thereby increasing the computational abilities without a loss of fault tolerance.

### The Benefits of the LEON3 Processor

Once the appropriate hardware paradigm has been chosen, the next consideration is choosing a high quality processor that has been proven in the space environment, and which can be modified in order to implement sufficient fault tolerance to resist the effects of radiation. The LEON3 processor, produced by Cobham Gaisler, is the focus of this thesis.

Although the radiation-hardened fault-tolerant version called the LEON3FT is expensive, the standard LEON3 version is open-source. The open-source version lacks built-in radiation-hardening or TMR architecture; however these features can potentially be implemented by the end-user. Due to the existing popularity of LEON for space missions, it is a proven technology for this application. By applying an existing fault mitigation approach developed at MSU to the LEON3, a low-cost equivalent to the LEON3FT can be produced.

### The Problem of Radiation in Space

The need for specialized computers for space-borne applications stems from the fact that there are much higher levels of ionizing radiation in outer space than are found on earth. This is because the earth is protected by its magnetosphere, which deflects or traps most of the harmful particles, as well as the earth's atmosphere, which attenuates

the energy of radiation that is not deflected before it reaches the earth's surface. However, once the surface of the earth is left behind, several different sources of ionizing radiation must be taken into account.

To interfere with the proper functioning of an electronic device, a source of radiation must be ionizing. This means that it either has enough energy to change the orbits of electrons, causing electron/hole pairs and resulting in excess charge in the circuit with the potential to alter proper electrical operation, or to break bonds, which may create permanent damage to the device structure. There are numerous types of particles, as well as electromagnetic radiation, with enough energy to have these effects. An example illustration of a radiation strike is shown in Figure 1:

Before detailing the different types of radiation, it is useful to cover a few important units and terms that are used to describe the intensity of radiation and the

durability of electronic components. An electron-volt is the most common term used to describe the energy levels of ionizing radiation. An electron-volt is equal to the amount of energy required to raise a single electron through a potential difference of one volt, or  $1 \text{ eV} = 1.6*10^{-19} \text{ J}$ . In general, to be considered ionizing, a radiation source must have an energy of at least 10 electron-volts (eV).

The other important measurement of radiation is the absorbed dose, which is the total amount of ionizing energy that the device has been exposed to per unit mass. Absorbed dose has units of rads, which is defined as 1 rad = an absorbed radiation dose of .01 J/kg [1].

The various particles that make up ionizing radiation come in different energy levels with corresponding amounts of damage potential, depending on their source. The least energetic particles are those trapped by earth's magnetosphere and the Van Allen Radiation belts. Although these particles are less energetic, they tend to be more numerous. Other particles move faster because they are part of the solar wind, and come from the sun. But the most energetic ionizing radiation comes from interstellar sources and tends to be travelling extremely fast.

#### Sources of Ionizing Radiation

The main sources of ionizing radiation are high-frequency electromagnetic waves, alpha particles, beta particles, protons, and neutrons. These sources and their associated energies (which correlate with their potential to cause damage) are listed in Table 1.

| Туре            | Description           | Energy                 |

|-----------------|-----------------------|------------------------|

| Gamma rays      | Very hi-freq EM       |                        |

| X-rays          | Hi-freq EM            |                        |

| Alpha particles | Helium-4 nuclei       | 5 MeV                  |

| Beta particles  | High-speed electrons, | $\leq 100 \text{ MeV}$ |

|                 | outer Van Allen belt  |                        |

| Trapped protons | inner Van Allen belt  | $\leq 100 \text{ MeV}$ |

| Solar protons   |                       | $\leq 1 \text{ GeV}$   |

| Neutrons        |                       |                        |

| Cosmic rays     | Extra-solar origin    | TeV                    |

Table 1. A listing of the major types of radiation and their energies [10].

High frequency electromagnetic radiation with enough energy to cause ionization includes x-rays, gamma rays, and some high-energy ultraviolet rays. Gamma rays often come in bursts all the way from other galaxies, and x-rays often have exotic interstellar sources as well. Gamma rays are very difficult to shield against, but are not as harmful as some other forms of radiation, as they are composed of electromagnetic radiation rather than particles.

Alpha particles, which are very energetic and high-speed helium-4 nuclei, are the byproduct of nuclear fusion reactions and make up part of the cosmic rays. Alpha particles are relatively easy to shield against, as they can be stopped by a sheet of paper.

Beta particles are high-speed electrons that are also produced by nuclear fusion in stars. They have more penetrative ability than alpha particles, but can still be stopped by a sheet of aluminum. There are large numbers of these in the outer Van Allen belt.

Another source of ionizing radiation is protons, of which there are many trapped in the inner Van Allen radiation belt. High-energy protons are sometimes produced by the sun as well. Neutrons are another source of radiation. Since they are electrically neutral, they tend to have less of a direct effect, and instead cause problems through secondary effects.

Cosmic Rays are very high energy particles that mostly originate in violent events outside of the solar system. This is not a specific type of particle but rather describes a category of origin and energy level. Cosmic ray particles have potentially the highest energy of the particles discussed here and therefore can be very dangerous.

### Causes of Variations in Radiation Levels

Spaceflights in Low Earth Orbit (LEO) such as those to the International Space Station (about 200-300 miles above the Earth) are largely protected from the radiation problem because most of the radiation is kept away from earth by the Van Allen radiation belts. The lower Van Allen belt is located between approximately 600 and 3,700 miles above the Earth's surface. Once at this altitude, however, the problem can become worse due to particles trapped in the belt. See Figure 2 on the following page.

Figure 2. Approximate locations of the inner (red) and outer (blue) Van Allen Radiation Belts around Earth. These belts protect electronics on Earth from most of the dangerous radiation found in space. Image Credit: NASA. [7]

Spaceflights in LEO are not entirely protected from radiation, however, and flight-critical computers require stringent radiation hardening measures even at this low altitude. One major cause of this is the South Atlantic Anomaly, an area located over South America and the southern Atlantic Ocean where the inner Van Allen belt drops down in altitude into the LEO altitude range.

The radiation problem also varies with time, especially as a result of sun cycles & Coronal Mass Ejections. During the peak of the solar cycle, there are more ultraviolet and x-rays emitted by the sun. Coronal mass ejections are enormous eruptions in the sun that occasionally produce large outbursts of protons and electrons. An interesting note is that designing a radiation-hardened computer system that can survive in space will not enable that computer to function everywhere in the solar system. By way of example, the magnetosphere of Jupiter is so strong that radiation levels there are many times higher than in Earth's Van Allen belts. A radiation-hardened computer system designed to survive in such an environment would need to be much more reliable than one designed for general-purpose space use.

### Types of Radiation-induced Damage

Radiation-induced damage is in general divided into two major categories: Total Ionizing Dose, which measures cumulative exposure, and Single Event Effects, which describe problems caused by excess charge created in the circuitry. Single Event Effects are then further divided based on severity. Space-borne computers must be able to handle both kinds of damage, although protection from the two types can vary drastically.

Total Ionizing Dose (TID) is the total absorbed dose of radiation that the electronic part has been exposed to over time. After a certain point, the buildup of radiation-induced damage in the semiconductor can influence the threshold voltages of the transistors and eventually cause some to stay permanently on, creating a short-circuit that can lead to permanent device failure.

The TID a device can absorb before failure is an important measure of radiation resistance. Fortunately, TID immunity tends to increase with smaller gate size technology. TID becomes a problem with an increase in trapped charge in oxide layers, an occurrence which decreases along with the thickness of the oxide. For this reason,

using a modern small gate size technology circuit can actually decrease susceptibility to TID-induced failure.

Single Event Effects (SEEs), on the other hand, are transient voltage fluctuations that are the result of a short-term radiation bombardment rather than a long-term buildup over time. Single Event Effects increase as the gate size decreases and come in different types, ranging in severity from harmless, to causing permanent device failure. An example of an ion strike creating unwanted charge in a silicon device is depicted in Figure 3 below.

Figure 3. Depiction of ion strike at a p-n junction creating separated charge carriers that, depending on other conditions, could cause one of the various types of Single Event Effects [8].

The three different types of Single Event Effects are described below:

Single Event Transient (SET) - in this event, high-energy radiation interacts with

the system and causes a short-term fluctuation in voltage or current. This will not

necessarily affect the operation of the circuit, however, unless the voltage fluctuation is

latched into a memory state or is used in a calculation before it dissipates. In this case it becomes a Single Event Upset (SEU).

Single Event Upset (SEU) – if a radiation strike causes a change in voltage that gets latched into memory, then a Single Event Upset is created. Although the computer chip is not permanently damaged, this type of event causes data corruption and requires the affected part of the chip to be scrubbed.

Single Event Functional Interrupt (SEFI) – a severe type of SEU in which the device's control circuit is placed into an illegal 'blocked' condition. This halts normal operation of the device and requires a power reset for recovery.

Single Event Latchup (SEL) – transistors short out, possible permanent damage. This type of event creates a short circuit between power and ground. In some cases the device will simply short out and need to be rebooted. In more extreme cases, however, the power drawn due to the short circuit can permanently damage the device. Therefore, this is the most extreme category of Single Event Effect [1].

#### TRADITIONAL SOLUTIONS FOR RADIATION

### Shielding

The most obvious and simple solution to prevent radiation damage is shielding. Shielding is commonly used in nuclear power plants and other earthbound radiation environments since it inexpensive and simple. Unfortunately, this is a difficult solution for use in outer space since the cost of launching the weight of the shielding into orbit is high. Furthermore, the effectiveness of shielding follows a logarithmic law, such that a thin piece of shielding material can stop low-energy radiation, but much thicker shielding is needed to stop higher-energy radiation. This effect is demonstrated in Figure 4 below:

Figure 4. Ionizing dose vs. Aluminum shielding thickness. Total dose cannot practically be reduced below a certain level, no matter how much shielding is added [16].

In order to for the shielding to be effective enough to allow continuous, uninterrupted operation of the underlying computing resources for mission-critical purposes, such a

high mass of shielding may be required as to make this option impractical or very expensive. Furthermore, shielding can sometimes make the radiation problem worse, since high-energy radiation can create secondary radiation particles upon striking the shielding. What is needed, then, is a circuit-level solution which modifies the computer circuit itself to create fault tolerance, therefore adding less weight to the design.

#### Circuit Level Solutions

There are three main categories of radiation-hardening techniques implemented on the circuit level. Although all three have been used in the past, they vary greatly in terms of cost and lead time to implement.

Radiation hardening by process (RHBP) is the most extensive and expensive means of radiation hardening. This method seeks to decrease the amount of defects present in the material through a carefully-controlled manufacturing process in order to decrease the amount of charge that will be trapped as a result of radiation bombardment. The downside of this technique is that it requires a significant change in the manufacturing setup. Therefore, it is more expensive since the economies of scale produced by standard chip manufacturing cannot be fully leveraged for making RHBP chips. Furthermore, there will naturally be a very long lead time for any improvements in this arena since new manufacturing processes and equipment would be needed.

The next option is radiation hardening by design (RHBD). In this method, the layout of the board is modified to mitigate the effects of radiation strikes by placing barriers between transistors. Two common methods for doing this are Local Oxidation of

Silicon (LOCOS) and Shallow Trench Isolation (STI). This is less expensive than RHBP because it does not require a separate process to produce, and can be manufactured on standard equipment. The downside is that additional chip space is required for the barriers. This extra distance can also potentially limit the clock speed of the circuit. See Figure 5 below for examples of RHBD.

Figure 5. Examples of radiation hardening by design, wherein a "guard ring" is placed around part of the transistor [9].

One of the major downsides of radiation hardening through process and design is long time I takes to develop these technologies, since completely new chip layouts and designs are required for new modifications. For this reason, such chips tend to lag several years behind their commercial, off-the-shelf (COTS), non-radiation-tolerant counterparts in terms of performance. This trend is shown in Figure 6.

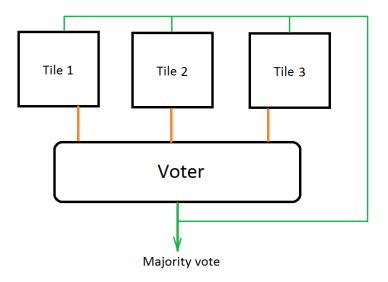

To overcome this inherent limitation in hardware development, the technique of radiation hardening by architecture (RHBA) has been developed. In this method, triple modular redundancy (TMR) is used to allow radiation resistance to be programmed into a traditionally manufactured device, at the expense of computing resources. This method is illustrated in Figure 7.

Figure 7. Basic setup of a triple-modular-redundant RHBA design.

Using this technique, three processors run in parallel, and a voter decides on the appropriate output. A radiation strike causing an error in a single processor will be overridden by the uncorrupted outputs of the other two processors. The faulted processor can then be corrected or reset as appropriate. Having a spare processor available (bringing the total to at least four) can dramatically reduce the time necessary to continue with calculations. The faulted processor can then be scrubbed in the background and reintroduced as a spare for future incidents.

#### EMERGING SOLUTIONS FOR RADIATION

#### FPGAs and Triple Modular Redundancy

Although Radiation Hardening by Process and Radiation Hardening by Design have many good qualities, they inherently involve hardware modifications, and therefore are more expensive and time-consuming to implement than Radiation Hardening by Architecture. Radiation hardening by Architecture, then, is the method of choice when an inexpensive, quick, and yet still reliable method is desired. The benefits of using this method are outlined below.

Although FPGAs tend to be more expensive than ASICs in general, radiationhardened FPGAs can be made much more inexpensively than radiation-hardened ASICs because radiation resistance can be implemented on a Commercial, off-the-shelf (COTS) FPGA using RHBA by simply reprogramming it to implement triple modular redundancy. On the other hand, a radiation tolerant ASIC must be designed and manufactured specifically for that purpose using RHBP or RHBD.

Radiation-hardened ASICs also have the downside of being very difficult to update or modify. Although new instruction code can be uploaded, the functional layout of the device will remain the same, and must generally be finalized months to years before implementation. An FPGA, on the other hand can be reprogrammed to utilize updated functionality even after launch. Use of FPGAs can also greatly reduce lead time for a project, since the hardware can be finalized before the actual FPGA synthesis. Therefore, the detailed design work to implement the configuration of the FPGA can take place much closer to the deadline since no hardware changes are involved.

FPGAs can be reconfigured upon startup so that the same processing real estate is optimized for different uses at different times. Yet, the FPGA is still more efficient than a traditional computer processor because it can be configured to efficiently perform the task at hand, and therefore is more similar to an ASIC in terms of data throughput, etc. Reconfiguration can also be used to replace or "scrub" the configuration in the FPGA to reset it to a known good state, although reconfiguring the entire chip at once would interrupt its ability to carry out the program.

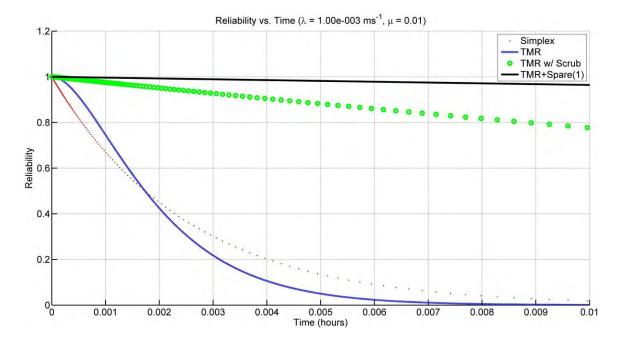

### Partial Reconfiguration and Scrubbing

Taking this a step further, partial reconfiguration allows for the change or reboot of only part of the FPGA processing resource independently of the rest. This allows the faulted portion of the FPGA to be reconfigured and reset while the rest of the FPGA resources continue to function. Partial reconfiguration also takes less time than full reconfiguration since fewer resources need to be written to. This could be a significant advantage in a high-radiation environment, where the time required to bring a spare processor back to a good state can have a large effect on the mean time to failure, as shown in Figure 8.

Figure 8. Introducing repair of faulted processor (green dots) greatly increases reliability over simple triple modular redundancy (blue line) [10].

The rewriting process of the FPGA resources is accomplished through "scrubbing", which can take the form of either blind scrubbing or readback scrubbing. In blind scrubbing, the entirety of the memory contents in the scrubbed region is overwritten whether the individual contents are faulty or not. Readback scrubbing, on the other hand, incorporates the ability to read the memory contents and compare them with a known golden copy to determine whether they need to be overwritten or not. The golden copy can potentially be stored in a medium less susceptible to radiation. Both methods of scrubbing allow for periodic refreshment of the FPGA contents, thereby greatly increasing the reliability of the system since faults can be removed. Readback scrubbing, however, is significantly more challenging to implement than blind scrubbing. The advantages of using FPGAs for radiation tolerant computing, then, are clear. There are two main design strategies that may be used to implement them: custom FPGAs with standard programming, and standard FPGAs running custom programming.

### Custom FPGAs with Standard Processors

There are currently multiple commercially available radiation-tolerant FPGAs on which one can run standard soft-core processors. The Virtex-QV series of boards by Xilinx is the industry leader in this category. A Virtex-5QV is shown below in Figure 9.

Figure 9. Virtex-5QV FPGA, the best rad-hard FPGA that money can buy [11].

Incorporating both RHBD & RHBA features, the Virtex-5QV series are the topof-the-line. Unfortunately, they are also expensive and somewhat difficult to obtain. With over 130,000 logic cells, this board has a TID capability of 1 Mrad and a SEL Immunity of 125 MeV-cm<sup>2</sup>/mg. These boards are designed such that any standard soft processor can be run on them. The Virtex-5QV, which is fabricated using 65 nm processes, is radiation hardened by design to guarantee TID up to 1 Mrad and single-event-latch-up (SEL) immunity. Since smaller process size automatically increases TID immunity, more modern 7-Series devices, fabricated using 28 nm processes, should have good TID immunity even without the special processes used to manufacture the Virtex-5QV. SEL immunity in the Virtex-5QV is enabled using a thin epitaxial layer in the wafer manufacturing process [5].

The Virtex-5QV chips are also designed with built-in Triple Modular Redundacy capability, so that the user's software is automatically triplicated and the output sent through a majority voter circuit. They also include Single Event Upset (SEU) correction.

The Virtex-5QV has been extensively tested and has already flown in space on the Sandia National Labs Materials International Space Station Experiment (MISSE-8) starting in 2011. During this experiment, the Virtex-5QV did not experience any singleevent upset errors [2]. The downside is that the Virtex-5QV is very expensive and somewhat difficult to obtain. For example, it is not available from the popular online electronics supplier, DigiKey. It may also be subject to ITAR regulations.

### Standard FPGAs with Custom Processors

Conversely, there are also radiation-resistant soft processors available that can be run on any standard FPGA. One of these is the LEON processor – a soft processor created by the European Space Agency and used in many space missions.

LEON is a 32-bit soft-core processor based on SPARC-V8 architecture. It was originally created by the European Space Agency in 1997 and later further developed by

Gaisler Research. There have been four versions released so far, with the most recent radiation-tolerant version being the LEON3FT. The LEON3FT offers built in fault tolerance using TMR and automatic error correction, but costs a good amount of money.

The LEON3FT can be implemented on both radiation-tolerant and conventional FPGAs. This can be a distinct advantage if there is any difficulty in procuring a radiation-tolerant FPGA.

The LEON processor is also a proven technology with a track record of successful space-borne implementation. The fault-tolerant version of the LEON2 processor has successfully been used in numerous space missions, including ESA's Alphasat telecom satellite, the Proba-V microsatellite, the Earth-monitoring Sentinel family and the upcoming BepiColombo mission to Mercury [3].

Another advantage of the LEON processor is that the non-radiation-tolerant version is open source and can be freely downloaded from the Cobham Gaisler website. Furthermore, the processor can be run on any brand of FPGA. This means that the LEON processor can be freely modified and ported to different platforms.

#### MSU'S APPROACH TO RADIATION TOLERANCE

#### Previous Work with MicroBlaze and Virtex-6

The team at Montana State University, Bozeman currently implements triple modular redundancy on a Xilinx Virtex-6 FPGA using Xilinx MicroBlaze soft processors. Nine MicroBlaze processors are placed on the FPGA, with three being active at any given time. This allows for a large number of spare processors, a potential advantage in a high-radiation environment. Additionally, a two-dimensional grid of radiation sensors is placed above the FPGA board to provide information about the environment over time, and also to help correlate any errors with their possible cause.

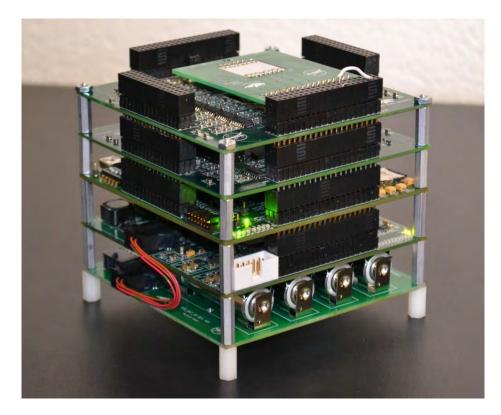

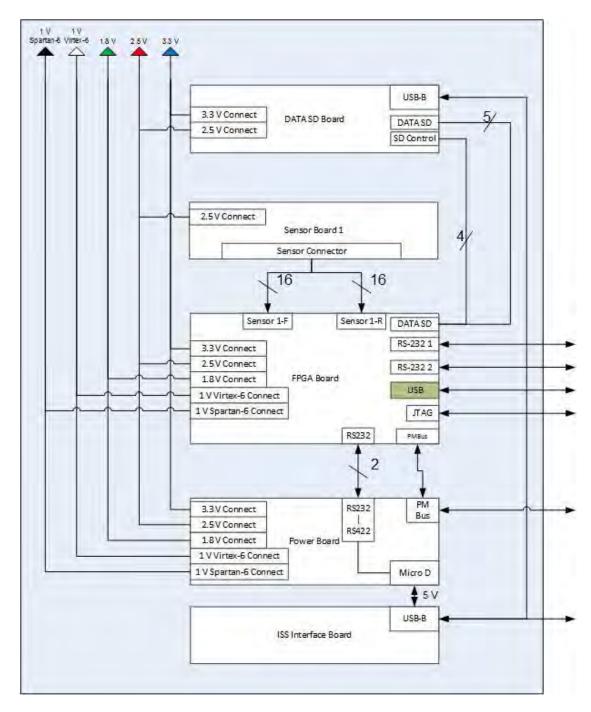

A great deal of research and design has been done by prior graduate students at MSU to design the hardware stack used to support the main FPGA in spaceflights. The MSU-designed hardware has flown in space multiple times, including on a NASA high altitude balloon and on a sounding rocket. The hardware has been designed to fit into the form factor of a 1U CubeSat to increase the ease of integration and availability of launch opportunities, and has outside dimensions are approximately 4"x4"x4". The CubeSat hardware stack used is shown in Figure 10.

Figure 10. Hardware stack used by the MSU research team [10].

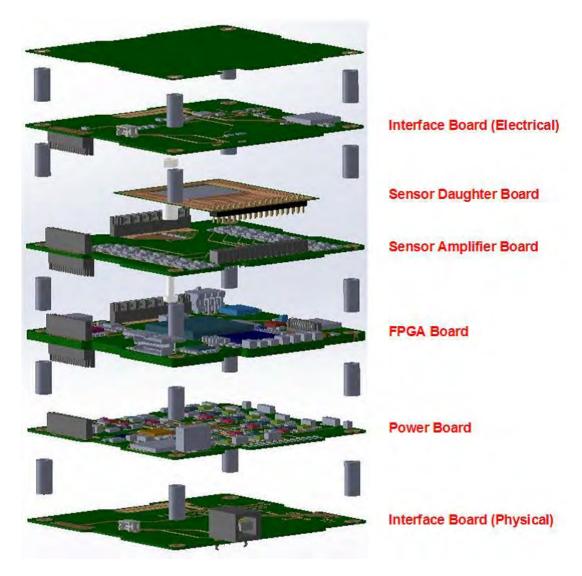

As can be seen, the flight hardware is divided into several separate but interconnected printed circuit boards that together allow the system to function autonomously during flight. Another view is shown in Figure 11, which delineates an exploded CAD model of the hardware stack.

Figure 11. Exploded CAD view of the MSU hardware stack [17].

A block diagram of the overall system is shown in Figure 12.

Figure 12. Block diagram of the MSU hardware stack [17].

The first individual part of the hardware stack under consideration is the power board, which must have low power consumption while offering power at several different voltages. There are currently eleven voltage rails on the power board in both digital and analog configurations. Additionally, the power board incorporates internal monitoring and fault protection [17].

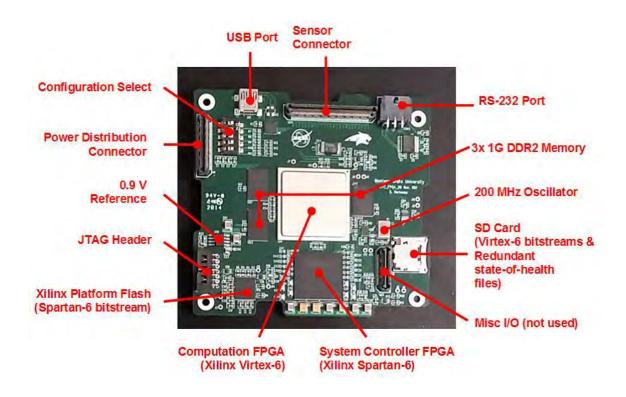

The FPGA board itself has also been the subject of a great deal of effort and redesign. There are two FPGAs located on this board, a main processor FPGA and a smaller control FPGA. The hardware stacks currently available use a Xilinx Virtex-6 for the main processor, although efforts are currently underway to transition to a Xilinx Artix-7. The control FPGA is a Xilinx Spartan-6, and is used to control the functioning of the main FPGA, as well as to write to it the full and partial bitstreams. The board holding the Virtex-6 and Spartan-6 FPGAs is shown in Figure 13 below.

Figure 13. FPGA board containing the main and control FPGAs used on previous flights [17].

If an error is detected in one of the processors running on the Virtex-6, blind scrubbing is used to write over that processor with a partial bitstream in order to return the processor to a clean state.

A MicroSD card is also included in the design as a storage device to hold the bitstream files as well as data collected during operation. Reading from and writing to the MicroSD card is controlled from the Spartan-6. Three 1 GB DDR2 RAM chips are also included on the FPGA board but are not currently used. In the future, however, these could be used to store larger programs and data, for example to enable the running of a Linux operating system on the processors. The system can be configured either through a complete bitstream loaded onto the Xilinx Platform Flash, which enables autonomous operation during spaceflight, or through a JTAG port, which is useful for debugging and system development [17].

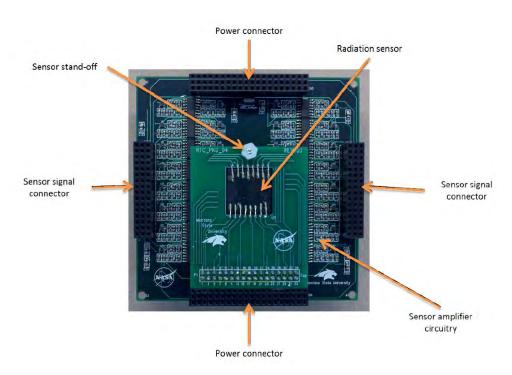

A custom radiation sensor and accompanying circuit board were designed and built by the MSU team in order to gather information during flight about the radiation environment. The radiation sensor circuit board is shown in Figure 14.

Figure 14. Radiation sensor and board developed by MSU [10].

The initial development of the radiation sensor contains 16 front-side channels and 16 back-side channels arranged perpendicular to each other, giving a total spatial resolution of 256 pixels [10].

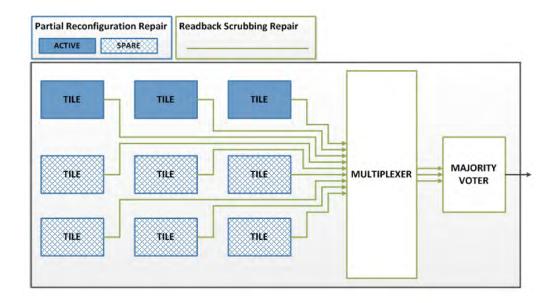

# Current Fault Radiation Tolerance Software

The current nine-tile TMR+spare architecture with partial reconfiguration runs on the main FPGA and has been developed over the last few years by several different graduate students. The MicroBlaze processors currently in use are 32-bit Harvard architecture soft-core processors. Nine MicroBlaze processors are placed on the main

29

FPGA, with three being active at any one time and up to six being held in reserve as spares. The setup of this system is illustrated in Figure 15 below.

Figure 15. The nine-tile TMR setup currently employed by the MSU system [10].

An important aspect of this system is the partial reconfiguration ability, which allows for the correcting of errors during operation and therefore a large improvement of mean time to failure. The only difference between MSU's approach and the system illustrated above is that blind scrubbing is used in place of readback scrubbing to fix faulted tiles.

One limitation of the current fault-tolerant setup is that only the main FPGA is triplicated. Neither the Spartan-6 control FPGA nor the memory holding the bitstreams are not triple modular redundant. Therefore, a radiation strike on the control FPGA or the memory could cause an unrecoverable error. However, once the proof of concept has been implemented on the main FPGA, it should not be conceptually difficult to apply the same setup to the rest of the design. As mentioned, there are three currently unused 1 GB DDR2 RAM chips on the FPGA board, so TMR memory could be implemented without requiring any hardware changes.

## Fault Tolerance Test Flights

The MSU team has flown the system into space multiple times already to test the radiation tolerance of the system in a realistic environment. Initial testing of the system took place at the Texas A&M Radiation Effects Facility in College Station, Texas using a 25 MeV Krypton radiation beam. This test proved that the radiation sensor and software systems worked, but did not produce actual faults in the MicroBlaze processors. The system was next flown on a high-altitude balloon in both 2012 and 2013 to measure its operation in an actual space environment. The first flight helped to uncover design flaws in the system, and the second flight went well, proving that the design was ready for spaceflight. However, no actual radiation strikes were recorded in either case [10].

Most recently, the system was launched as part of the payload of a NASA-funded sounding rocket in October of 2014. The rocket launch is shown in Figure 16 below.

Figure 16. NASA-funded sounding rocket that sent the MSU radiation tolerant computer to space in October 2014 [20].

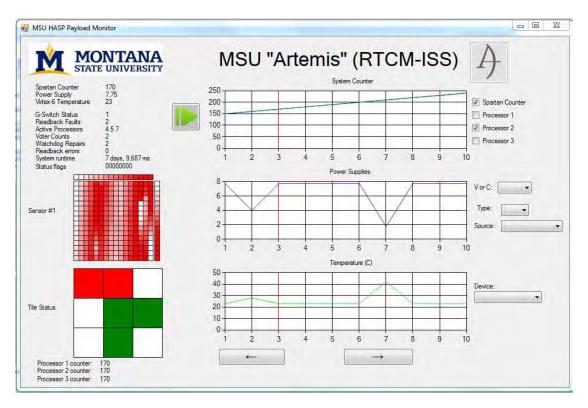

The system that flew in October 2014 was in space for a few minutes and ran the MicroBlaze and Virtex-6 system described above. Data concerning radiation strikes, system power levels, and program outputs was logged during flight and written to the MicroSD card. This data was then analyzed post flight using a custom-made Graphical User Interface (GUI). A screenshot of this GUI (showing sample rather than actual flight data) is shown in Figure 17.

Figure 17. Sample screenshot of the GUI used to view MSU flight data.

Building on the lessons learned from the 2014 flight, the MSU team is updating the system and plans to operate it for several months aboard the International Space Station (ISS) in 2016. Due to limited power available to experiments onboard the ISS, the hardware is being modified to use an Artix-7 FPGA instead of a Virtex-6. Although work is also underway to replace the MicroBlaze processor with the LEON processor, this transition is not expected to be completed in time for the flight to the ISS.

#### Transition to LEON3 and Artix-7

The MicroBlaze processor works for the present but the next step is to implement a fault-tolerant architecture on a proven space processor. For this work, the LEON3 processor has been chosen. LEON is open-source and can be freely ported to any FPGA platform. The LEON soft processor is furthermore already one of the standards in the space industry, making it a logical next step to implement. By applying MSU's faulttolerant architecture to the LEON3 to implement triple modular redundancy (TMR), a low-cost near-equivalent to the LEON3FT can be produced.

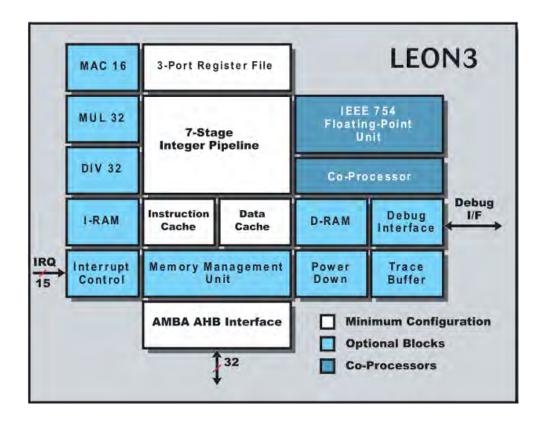

The LEON3 processor uses a robust and large architecture (compared with the MicroBlaze processor), which is good for running real space missions but makes it more difficult to convert into a reconfigurable design that fits onto an FPGA board. The LEON3 is a 32-bit SPARC version 8 compliant processor, meaning that it uses a reduced instructions set architecture (RISC). It also incorporates a 7-stage pipeline, separate instruction and data caches of the Harvard architecture, an AMBA-2.0 AHB bus interface, and has a high performance of up to 1.4 DMIPS/MHz [15].

Furthermore, MSU is transitioning to using an Artix-7 FPGA in place of the Virtex-6. The two FPGAs have a similar amount of resources available, but the Artix-7 uses far less power, which can make a large difference on power-limited space missions. Furthermore, it allows synthesis and implementation using Xilinx Vivado Design Suite as opposed to the older Xilinx ISE Design Suite. Vivado is more modern and includes a streamlined interface that can greatly increase productivity.

### The Artix-7 FPGA

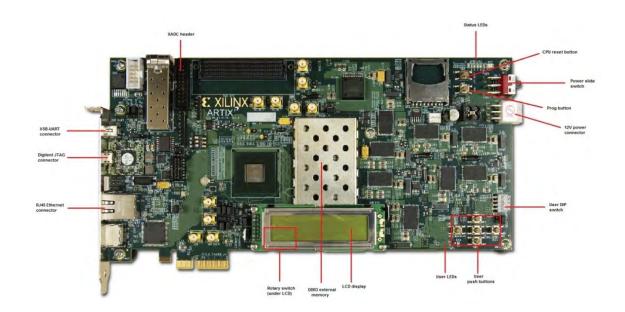

The new FPGA being incorporated by the MSU Research Team is an Artix-7 200T. An AC701 Evaluation Board containing the same FPGA is also in the lab and was used in this project. Such an evaluation board is shown below in Figure 18.

Figure 18. An AC701 development board identical to the one used for this project [12].

The Artix-7 is part of the Xilinx 7 series FPGA family, which was released in 2010 and uses a 28 nm die process. The Artix family is optimized for low power usage and cost. The 200T model, used in the MSU design, is the largest available Artix-7 FPGA. It contains 215,360 logic cells arranged in 33,650 slices, and 13,140 kB of block RAM. Each slice contains four LUTs and eight flip-flops [19].

#### FAULT TOLERANCE APPROACH FOR A LEON3 ARCHITECTURE

### The LEON3 Architecture

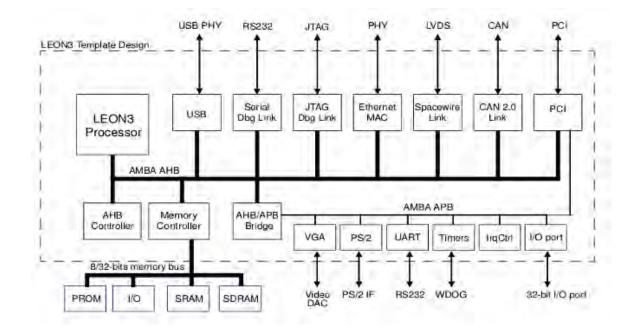

A general diagram of the components contained within the LEON3 processor is shown in Figure 19 below.

Figure 19. Block diagram of a full LEON3 processor including peripherals [14].

As shown in the above diagram, all of the components of the LEON processor are connected via the AMBA AHB bus. To save space on the FPGA, unneeded components may be turned off. These include the Ethernet MAC and Serial Debug Link. The vital components that must be kept are the JTAG Debug Link, the AHB bus, some on-board SRAM, and four CPUs. All components are connected via the AMBA AHB bus. A more detailed diagram showing only a CPU of the LEON3 is given in Figure 20.

Figure 20. Diagram of a LEON3 CPU [14].

To fit four reconfigurable CPUs within the limited resources of a reasonably-priced FPGA board, only the "Minimum Configuration" blocks shown in white in addition to the "Debug Interface" should be implemented.

The LEON3 is open-source and can be modified and run on any FPGA. This is advantageous because it offers flexibility in the choice of future hardware. The LEON processor may also offer improved performance over the MicroBlaze processor. According to a Master's Thesis study of the subject done by Mattsson and Christensson in 2004, the LEON processor has better performance than the MicroBlaze processor [4].

### Cobham Gaisler Components

This section describes the Cobham Gaisler supplied tools which are available with the LEON processor and which can all be implemented in a Linux environment to assist in development of the LEON3. Unfortunately, the USB drivers to connect to the board are very difficult to install properly for Linux. Therefore, the GRMON2 debug tool was used on Windows 7 instead.

GRLIB Processor Files are pre-defined files that can be used to create a LEON processor that can run on any of the supported Development Boards. They contain the entire source VHDL code needed to compile a full LEON processor, including all code for the memory modules. Support for numerous boards, including both Xilinx and Altera, is included. The "xconfig" graphical configuration tool is also available as a way to easily modify the design of the processor, and to turn different components on or off.

The BCC cross-compiler can be downloaded from the Gaisler website in order to compile C code to run on the LEON processor. Based on the standard Linux GCC compiler, BCC is necessary in order to compile code that can be run properly on LEON. Writing application software and compiling it with BCC Compiler is straightforward; for this project both a simple "Hello World" program and a simple "Counter" program were written. LEON is also capable of running a full-fledged Linux operating system, a sample of which can also be downloaded from the Gaisler website.

The TSIM ERC32/LEON Simulator is a simulator made especially for LEON. It was used to verify correct operation of the "Hello World" program on an unmodified

LEON processor. However, it was unclear how to run simulations based on modified LEON code, and this software was not used to test the final design.

Finally, GRMON2 is a non-intrusive debugging monitor provided by Cobham Gaisler that allows for observation of LEON processor resources. It also allows read and write access to all registers and memory.

If the professional version of GRMON2 is purchased, error injection to simulate radiation strikes is also supported. According to the GRMON User's Manual, "An injected error flips a randomly chosen memory bit in a [sic] one of the memory blocks, effectively emulating an SEU" [13]. If this could be implemented with a 4-core LEON processor, a good proof-of-concept could be verified.

### **LEON Implementation Instructions**

The following paragraphs outline the basic process of getting the LEON3 software functioning on an AC701 development board with an Artix-7 processor. Other boards can be used as well; LEON3 comes preconfigured with basic implementations for numerous board choices. See Appendix A for more detailed instructions on implementing a LEON3 system, as well as for links to websites for downloading the various required files.

The two main things necessary are the LEON3 "grlib" software suite, downloadable directly from Aeroflex Gaisler's website, and, if development on a Xilinx Series 7 board is desired, Xilinx Vivado Design Suite. There are other software packages that can be downloaded from Gaisler as well, including a LEON-specific compiler, the TSIM simulator, and the GRMON debug tool. These tools were described in more detail in the previous section.

Although in theory Cobham Gaisler's "GRTools" software can be used to develop LEON in a Windows environment, in practice, synthesizing the LEON requires Linux. This project used SUSE Linux Enterprise Desktop version 12, although Red Hat and Ubuntu also work. Installing Linux and setting up the Xilinx toolchain therein are described in detail in Appendix A. Unfortunately, although Linux and the required Xilinx software were successfully installed, the drivers were not able to talk to the FPGA from the Linux computer. Therefore, actual downloading of the bitstream and communication with the board using GRMON was done from a computer running Windows 7.

The specific steps required to build and synthesize the LEON3 processor can be confusing since instructions vary for different FPGAs. Fortunately, the Artix-7 board uses Vivado Design Suite, which enables the entire synthesis, implementation and bitstream generation process to be run from the Vivado GUI, obviating the need for complex command line instructions. Simply add the appropriate paths for Vivado and ISE and then run "make vivado-launch" in the terminal to open Vivado, and work from there. For more detailed instructions, including instructions for making the LEON CPUs reconfigurable and for implementing Triple Modular Redundancy, see Appendix A. Instructions relating to implementing a similar design on a Virtex-6 FPGA may be found in Appendix B.

40

### EXPERIMENTAL RESULTS

Four different configurations of the LEON processor were implemented. They are described below, in order of increasing complexity. For the first three designs, no changes are required to the VHDL code downloaded as part of the GRLIB library from Cobham Gaisler. All that is needed is to choose the appropriate option for the number of CPUs in the Gaisler "xconfig" GUI, as well as to place and make reconfigurable the CPUs in the Vivado GUI when appropriate. To emulate conditions on the actual hardware stack, in all designs the external memory controller is turned off and 128kB of on-chip SRAM is used instead, starting at memory location 0x40000000. All four designs were implemented on an Artix-7 XC7A200T-2FBG676C FPGA at a steppeddown clock speed of 100MHz.

# Single Core LEON

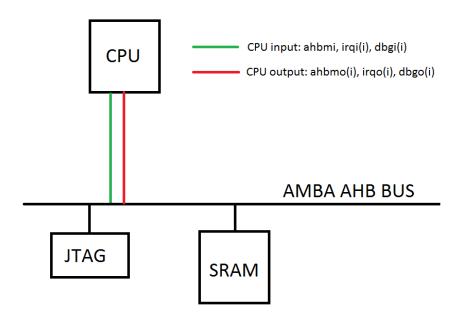

This is the simplest instantiation of the LEON3 processor, requiring no special modifications. A block diagram of this configuration is shown in Figure 21.

Figure 21. Block diagram of a single core LEON processor.

The resource usage on the Artix-7 FPGA is shown in Figure 22 below:

| Resource   | Utilization | Available | Utilization % |

|------------|-------------|-----------|---------------|

|            |             |           |               |

| FF         | 2964        | 267600    | 1.11          |

| LUT        | 6714        | 133800    | 5.02          |

| Memory LUT | 11          | 46200     | 0.02          |

| I/O        | 16          | 400       | 4.00          |

| BRAM       | 76          | 365       | 20.82         |

| BUFG       | 2           | 32        | 6.25          |

| PLL        | 1           | 10        | 10.00         |

Figure 22. Resource usage of a single core LEON processor on Artix-7 FPGA.

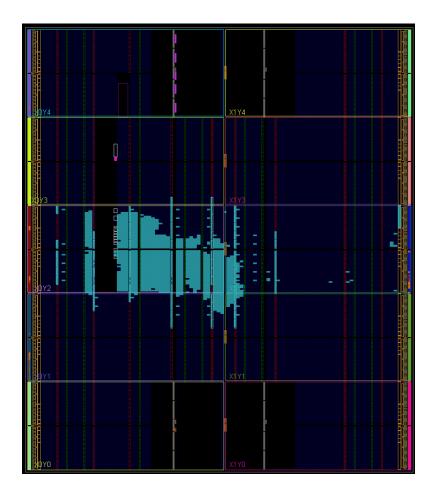

The implemented floorplan is shown in Figure 23.

Figure 23. Implemented single core LEON processor on Artix-7 FPGA.

As shown above, the single core design without partial reconfiguration easily fits onto the FPGA and uses a small amount of the available resources. Note that the implemented design clusters near the X0Y2 clock region, which contains the JTAG communication pins.

# Four Core LEON

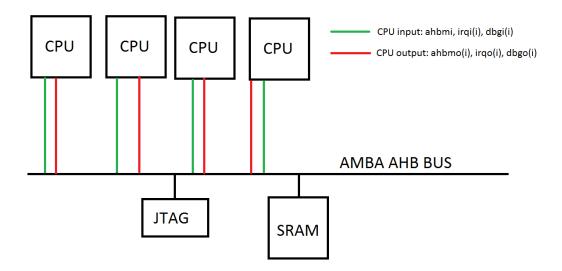

This design is identical to the previous one, except that there are four CPUs instead of one. A block diagram of this configuration is shown in Figure 24.

Figure 24. Block diagram of a four-core LEON processor.

The resource usage on the Artix-7 FPGA is shown in Figure 25 below:

| lization - Post-Implementation |             |           |               |

|--------------------------------|-------------|-----------|---------------|

| Resource                       | Utilization | Available | Utilization % |

| FF                             | 7383        | 267600    | 2.76          |

| LUT                            | 21071       | 133800    | 15.75         |

| Memory LUT                     | 41          | 46200     | 0.09          |

| I/O                            | 21          | 400       | 5.25          |

| BRAM                           | 112         | 365       | 30.68         |

| BUFG                           | 2           | 32        | 6.25          |

| PLL                            | 1           | 10        | 10.00         |

Figure 25. Resource usage of a four-core LEON processor on Artix-7 FPGA.

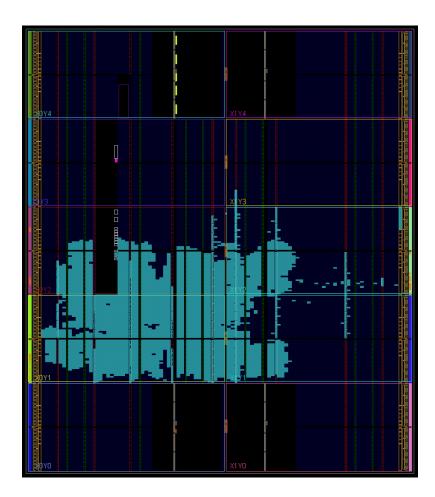

The implemented floorplan is shown in Figure 26.

Figure 26. Implemented four-core LEON processor on Artix-7 FPGA.

As shown, the four-core LEON uses moderately more resources than the single core version, but still easily fits onto the board.

### Four Core, Reconfigurable LEON

The next step involves introducing the ability to independently reconfigure each of the four CPUs. In order to fit this configuration onto the Artix-7 FPGA, the "Minimal" CPU was chosen with the Floating Point Unit option excluded, but the Debug Support Unit included (for ease of comparison, this configuration was used in all four versions). This configuration includes separate 8kB instruction and data caches in each CPU. Each of the four CPUs was assigned to two clock regions, with one CPU placed in each of the four corners of the chip. A block diagram of this configuration is shown in Figure 27 below:

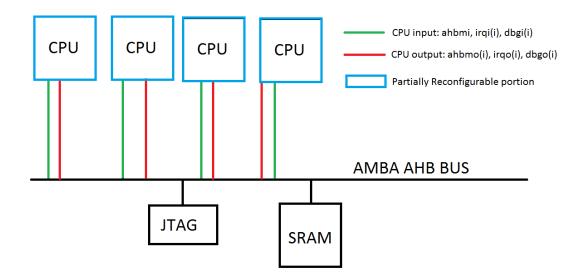

Figure 27. Block diagram of a four-core, partially reconfigurable LEON processor.

The resource usage on the Artix-7 FPGA is shown in Figure 28 below.

| Resource   | Utilization | Available | Utilization % |

|------------|-------------|-----------|---------------|

| FF         | 7485        | 267600    | 2.80          |

| LUT        | 55180       | 133800    | 41.24         |

| Memory LUT | 29          | 46200     | 0.06          |

| I/O        | 21          | 400       | 5.2           |

| BRAM       | 112         | 365       | 30.68         |

| BUFG       | 2           | 32        | 6.2           |

| PLL        | 1           | 10        | 10.00         |

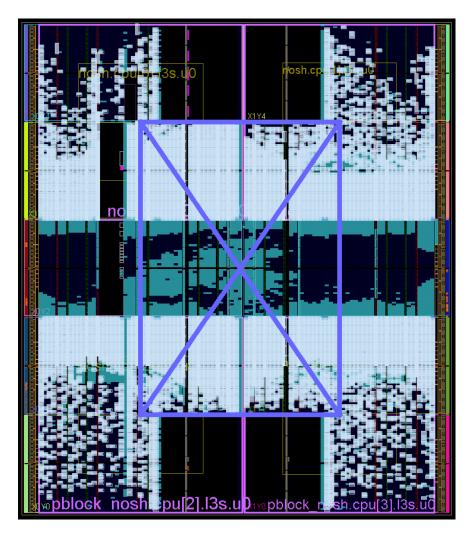

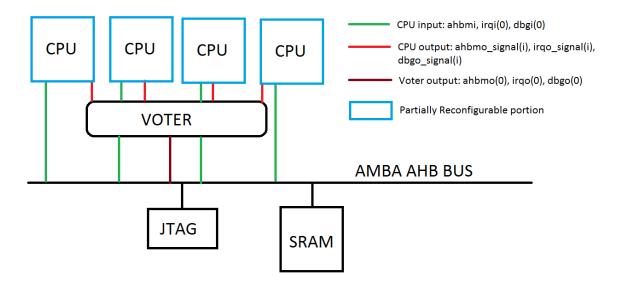

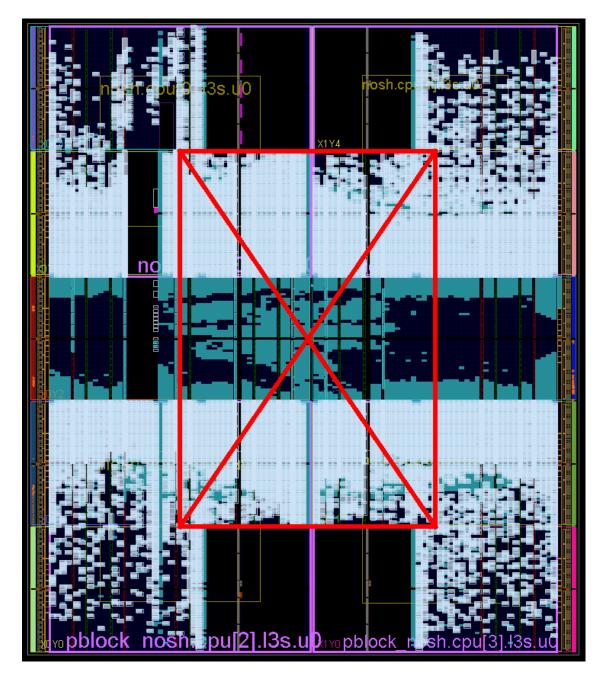

Figure 28. Resource usage of a four-core, partially reconfigurable LEON processor on Artix-7 FPGA.