### **DesignConEast 2005**

Track 4: Power and Packaging (4-WA1)

# Design of a Low-Power Differential Repeater Using Low-Voltage Swing and Charge Recycling

**Authors:** Brock J. LaMeres,

**University of Colorado** /

Sunil P. Khatri

**Texas A&M University**

### **Problem Statement**

- Power is the largest problem facing IC/SoC designers

- On-chip trace delay limits performance in DSM

- 1) Repeaters are used to reduce delay

- 2) Repeaters add power

### Agenda

- 1) Problem Motivation

- 2) Proposed Solution

- 3) Simulation Results

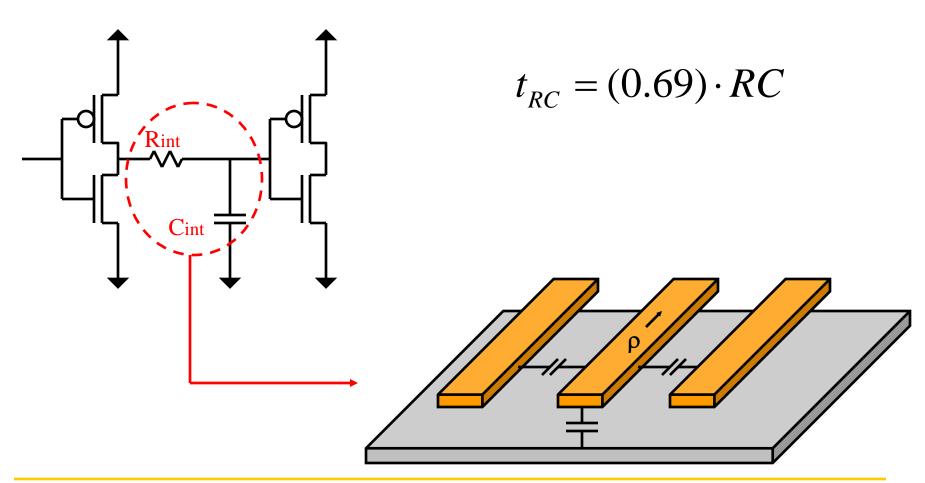

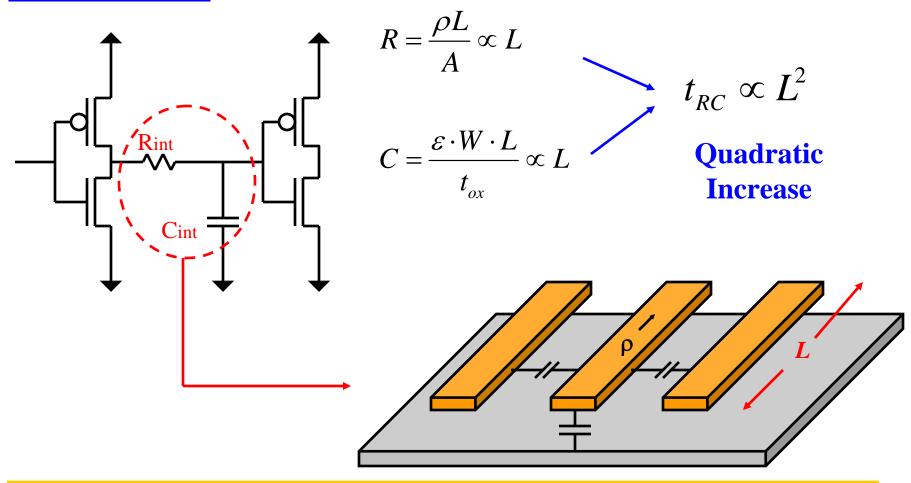

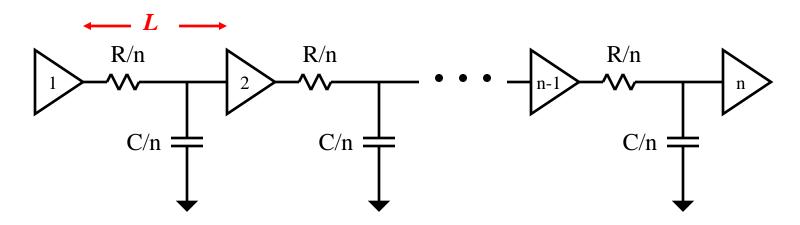

### **RC Trace Delay**

### **RC Trace Delay**

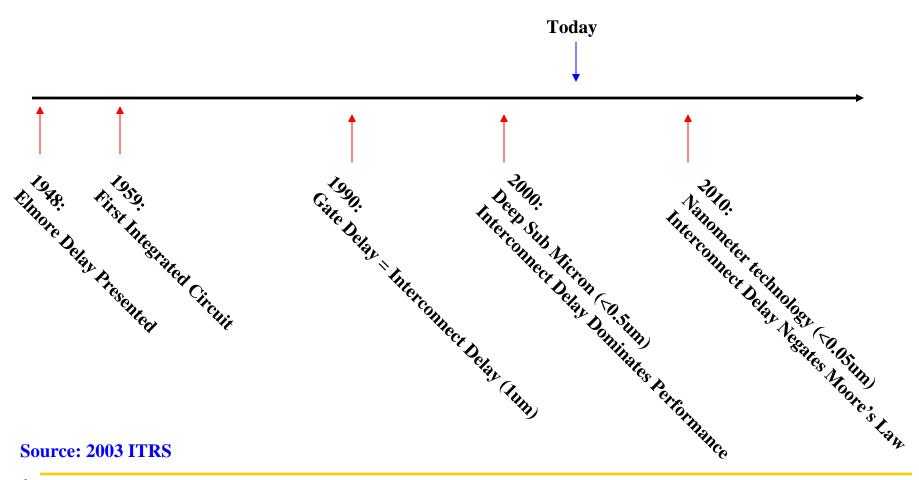

#### **Interconnect Dominates DSM Performance**

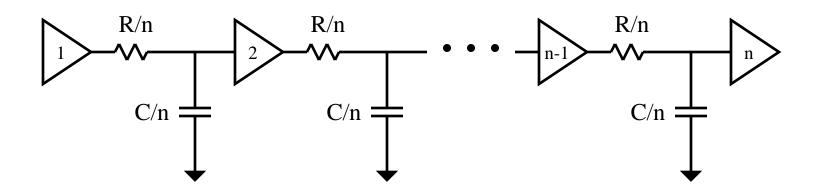

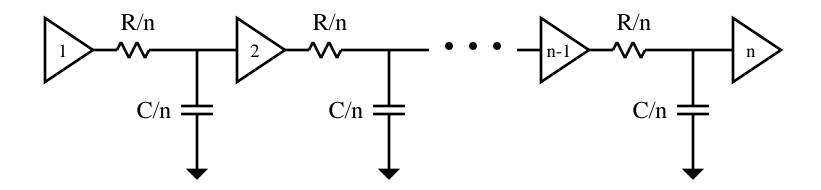

**Standard Solution:** "Repeater Insertion"

- Break line into smaller segments:

- $(L \rightarrow 0)$   $t_{buf} = t_{RC}$ • Optimal sizing when:

- Linear dependence:

#### **Repeaters Add Power**

$$P_{dynamic} = C \cdot V_{swing}^2 \cdot f$$

$$P_{\textit{short-circuit}} = I_{\textit{sat}} \cdot V_{\textit{DD}} \cdot f$$

**Power**  $\propto$  (# of Repeaters)

#### **Repeater Power Scaling Isn't Realistic**

#### **2003 ITRS Prediction:**

• at 50nm, global interconnect will consume 40% of power in VLSI

• 0.25 um uP : 50,000 repeaters : 8 Watts • 70 nm uP : 700,000 repeaters : 60 Watts

#### **Need to Reduce Power**

- Need techniques to reduce power of repeater scheme

- A small decrease in delay is acceptable

- Net improvement in PDP is the goal

#### **Current Trends**

- Differential signaling on clock traces for Noise Immunity

- Well Suited for Low-Voltage Output Swing

- Well Suited for Charge Sharing

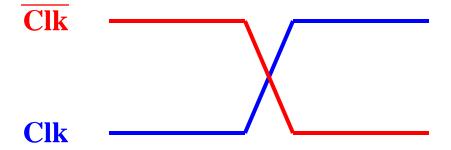

#### **Differential Signaling**

- Complimentary Outputs for VLSI CMOS

- Receiver Performs (CLK-CLK) which rejects coupled noise

- Receiver Performs (CLK-CLK) which doubles effective amplitude

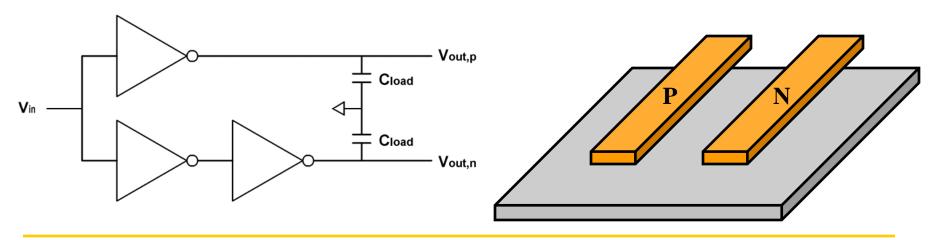

#### **Low-Voltage Swing Outputs**

• Reducing Output Swing Reduces Power

$$P_{dynamic} = C \cdot V_{swing}^2 \cdot f$$

Quadratic Decrease!!!

• Differential Signaling has extra margin to accommodate this

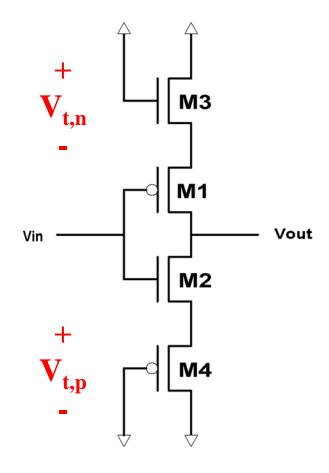

#### **Low-Voltage Swing Outputs**

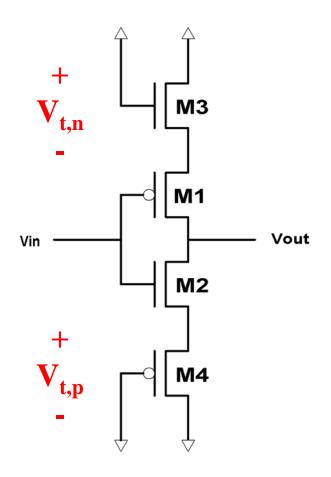

- $\bullet$  Typical CMOS swings from  $V_{SS}$  to  $V_{DD}$

- Insert  $V_t$  drops between supplies to reduce output swing

#### **Low-Voltage Swing Outputs**

• The reduced output swing is:

$$V_{LV-swing} = V_{DD} - V_{t,n} - |V_{t,p}|$$

• The reduced power is:

$$P_{dynamic} = C \cdot V_{LV-swing}^2 \cdot f$$

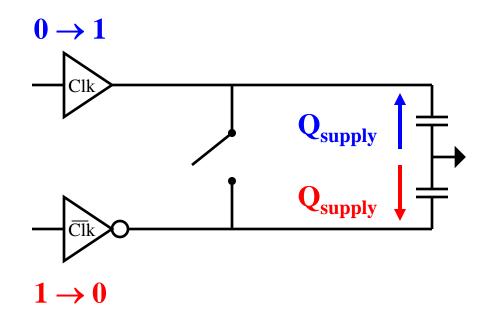

#### **Charge Recycling**

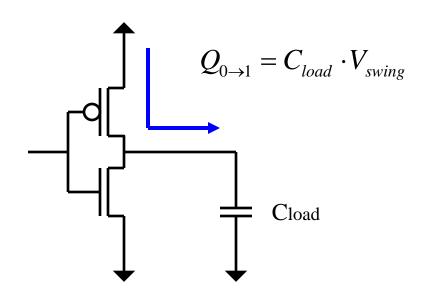

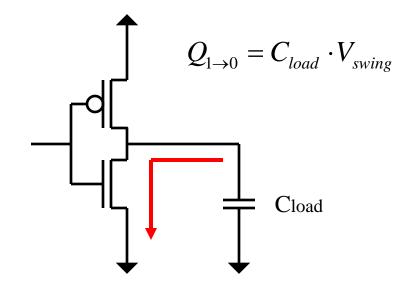

• Typical CMOS charges output from supply

$0 \rightarrow 1$  Transition

$1 \rightarrow 0$  Transition

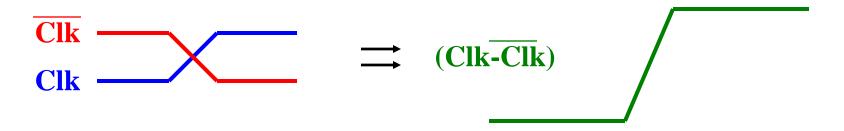

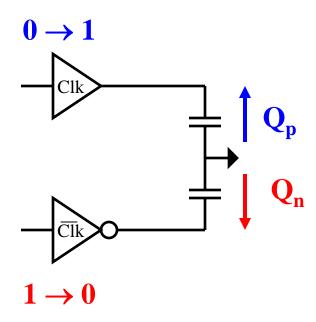

#### **Charge Recycling**

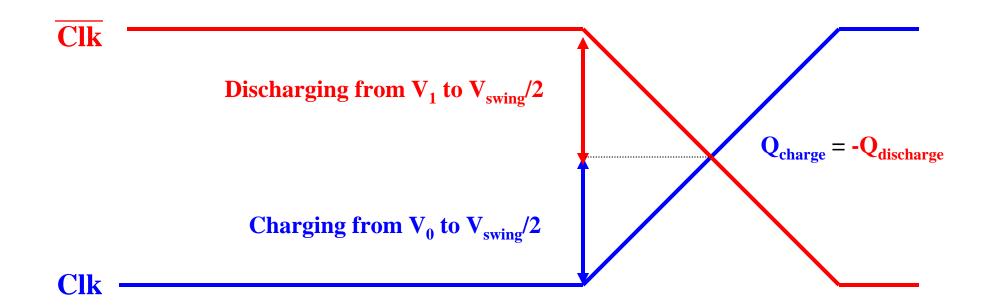

• The Symmetry of Differential Signaling can be exploited

One Driver is always charging while the other is discharging

### **Charge Recycling**

• During first half of the transition equal charge is distributed

### **Charge Recycling**

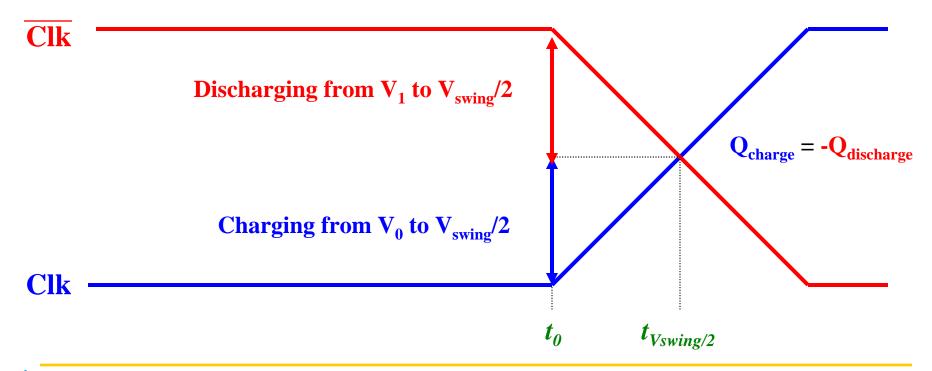

• Charge can be "Shared" between Clk &  $\overline{\text{Clk}}$  from  $t_0$  to  $t_{Vswing/2}$

### **Charge Recycling**

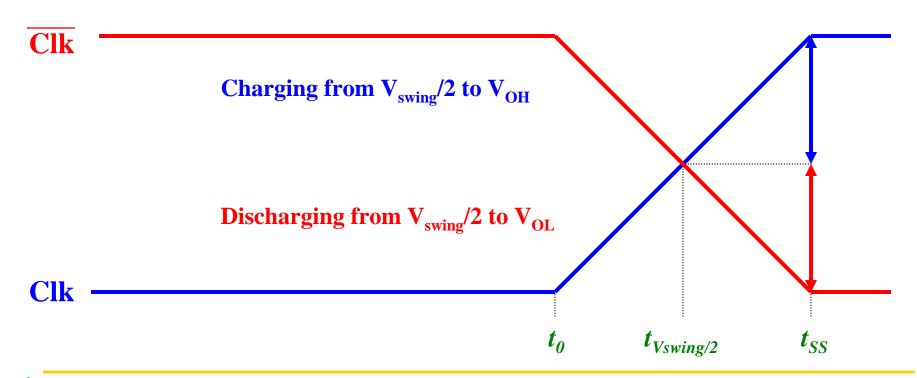

ullet From  $t_{Vswing/2}$  to  $t_{SS}$  charge is provided by Supplies as usual

### **Charge Recycling**

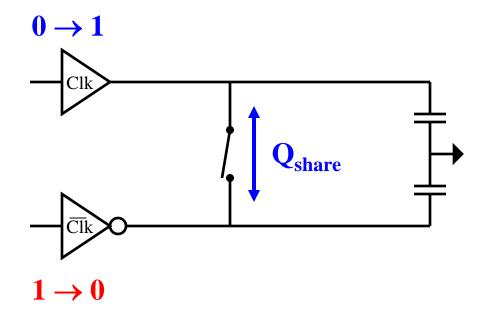

• Clk & Clk are connected from  $t_0$  to  $t_{Vswing/2}$

### **Charge Recycling**

ullet Clk & Clk are disconnected from  $t_{Vswing/2}$  to  $t_{SS}$

### **Charge Recycling**

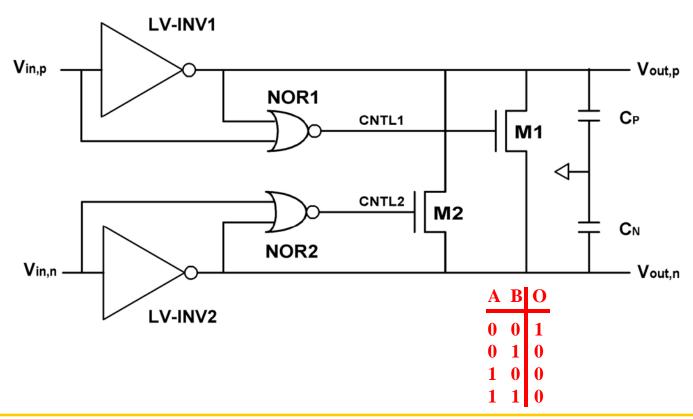

### • Circuit Description

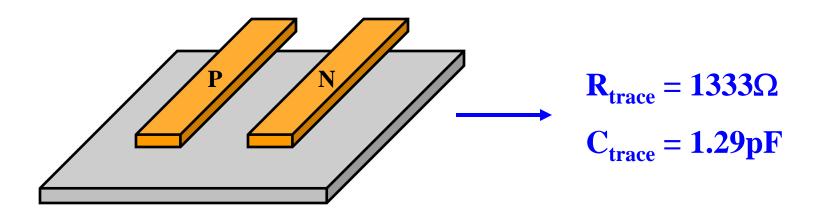

### **Trace Modeling**

- BSIM 0.1um Process (BPTM)

- 1cm Length

- Metal 3

### **Repeater Design**

### **Using Optimal Sizing:**

| • Full-Swing Repeater:                   | 15 |

|------------------------------------------|----|

| • Low-Voltage Repeater:                  | 9  |

| • Low-Voltage Charge Recycling Repeater: | 9  |

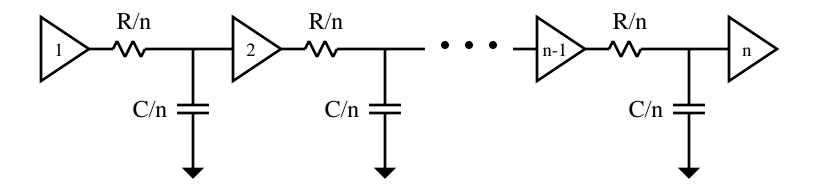

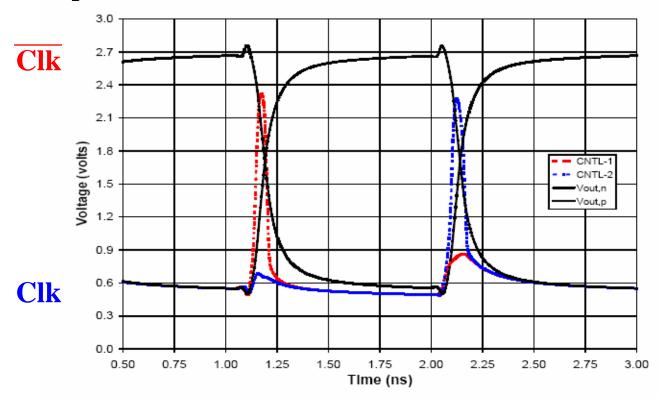

### **Circuit Operation**

#### • Circuit Operation

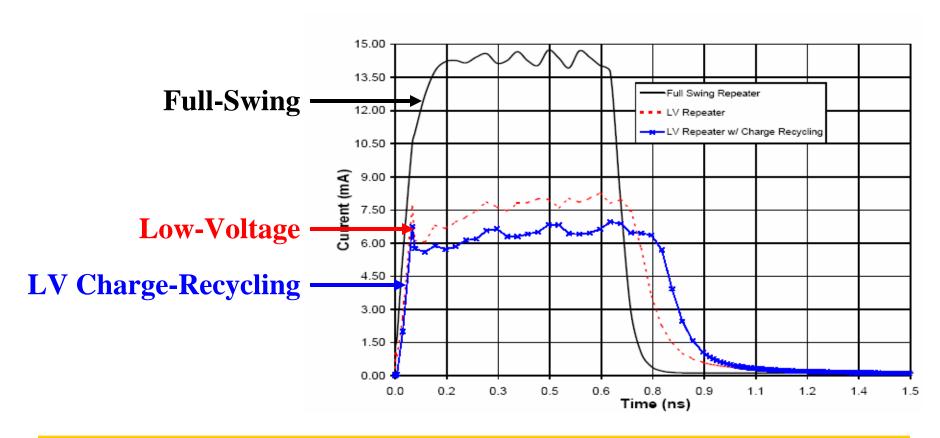

#### **Current Profile vs. Time**

#### **Performance**

#### **Both Improve PDP**

| Circuit                               | Figures of Merit |            |               | Improvement |           |       |               |

|---------------------------------------|------------------|------------|---------------|-------------|-----------|-------|---------------|

|                                       | Delay (ps)       | Power (mV) | PDP (ps · mV) | Delay (%)   | Power (%) | PDP ( | (%)           |

| Full-Swing Repeater                   | 639              | 12.06      | 7.71          | -           | -         | -     | $\overline{}$ |

| Low-Voltage Repeater                  | 699              | 7.54       | 5.27          | -9          | 37        | 32    | 1             |

| Low-Voltage Charge Recycling Repeater | 774              | 6.92       | 5.36          | -21         | 43        | 31    | .!            |

- Lowest Delay = Full-Swing Repeater

- Lowest PDP = Low-Voltage Repeater (32% improvement)

- Lowest Power = Low-Voltage Charge Recycling Repeater (43% improvement)

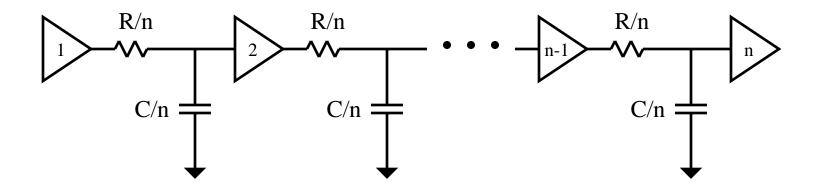

### **Implementation Details**

#### **Suggested Use**

• On-Chip Metal 3 or Greater

#### **Not Suggested**

• On-Chip Metal 1 or 2

(too much resistance, acts distributed)

Off-Chip

(too much inductance, acts distributed)

### **Implementation Details**

### **Sizing**

| Circuit          | Section    | Transistor | Size     |                          |

|------------------|------------|------------|----------|--------------------------|

| Full-Swing       | INV        | NMOS       | 2.5/0.1  |                          |

| Repeater         |            | PMOS       | 8.0/0.1  |                          |

|                  | INV        | NMOS       | 5.0/0.1  |                          |

| Low-Voltage      |            | PMOS       | 16.0/0.1 |                          |

| Repeater         | $V_t$ Drop | NMOS       | 25/0.1   | - Low Resistance         |

|                  |            | PMOS       | 80/0.1   |                          |

|                  | INV        | NMOS       | 5.0/0.1  | - Negligible Capacitance |

|                  |            | PMOS       | 16.0/0.1 |                          |

| Low-Voltage      | $V_t$ Drop | NMOS       | 25/0.1   |                          |

| Charge Recycling |            | PMOS       | 80/0.1   |                          |

| Repeater         | NOR        | NMOS       | 0.2/0.1  |                          |

|                  |            | PMOS       | 0.8/0.1  |                          |

|                  | CS         | NMOS       | 0.2/0.1  | $<$ (20%) $\tau_{load}$  |

### Summary

### **Trends**

- Power and Delay are major problems in DSM

- Repeaters are expected to dominate power

- Differential signaling is being used for noise immunity on clocks

#### **Proposed Technique**

- Low-Voltage Swing enabled by differential signaling

- Charge Recycling enabled by differential signaling

- Suffer small delay penalty for decreased power (PDP ↑)

## **Questions?**